QuadrantLatch.v

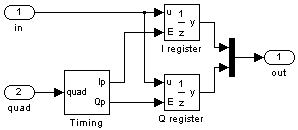

This module latches the I and Q parts of an interleaved I/Q data stream given a quadrant fiducial, optionally averaging the samples. The diagram shows the basic structure without averaging.

Ports

| clk | input | The clock input. |

| in | input | The I/Q signal to be sampled. |

| quad | input | The quadrant fiducial. The I part is sampled when quad = 002 and Q when quad = 012. |

| out | output | A double-width output consisting of the sampled I and Q parts. |

Parameters

| w1 | Width of the input port (default 16). |

| w2 | Width of the output port (default w1). |