This module multiplies two multiplicands and sums their product into an accumulator. Unlike the Accumulator module, this module accumulates on each clock cycle an enable input is asserted witout termination condition. The depth of the accumulator, input and output bit widths, an overflow bit width, and clippling of least-significant bits (lsbs) may be specified. The most-significant bit of the output is aligned with the top of the accumulator. An input resets the state of the instance.

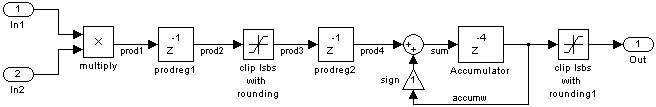

Ports | Parameters | Notes | Example | Detail block diagram

| clk | input | The clock input. |

| reset | input | Reset input, which clears the accumulator and registers. |

| en | input | The enable input. An addition to and shift of the accumulator occurs when this signal is high. |

| in1 | input | The first multiplicand. |

| in2 | input | The second multiplicand. |

| out | output | The output port. The last outdepth registers of the accumulator are available at this port, with the last occupying the least-significant bits of the port. |

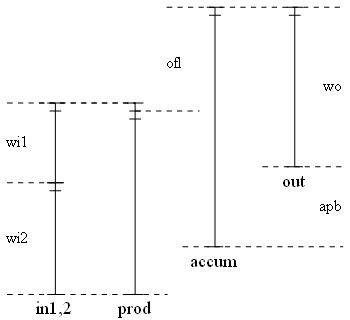

The figure to the right illustrates bit alignments and meanings of the bit-width parameters.

| wi1 | The bit width of the first input port (default 11). |

| wi2 | The bit width of the second input port (default 12). |

| wo | The bit width of the output port (default 19). |

| ofl | The number of overflow bits (default 4). The number of accumulation clocks is tied to this parameter: cycles = 2ofl. |

| apb | The number of accumulator precision bits (default 5). These bits on the lsb end of the accumulator participate in the addition of samples, but are discarded at the end of the cycle. This is done to discard accumulated quantization noise in lsbs while preserving precision of the output. |

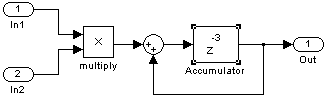

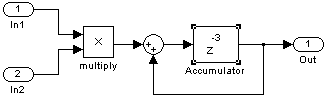

| depth | The depth of the accumulator is shown in the diagram above as '3'. The default is 1. |

| sign | The sign of the accumulate sum, as show in the detailed block diagram below. Use minus to subtract. The default is plus. |

| outdepth | The number of registers of the accumulator that are available at the out port. This parameter counts from the last (right-most) registers with the last occupying the least-significant bits. The default is 1. |