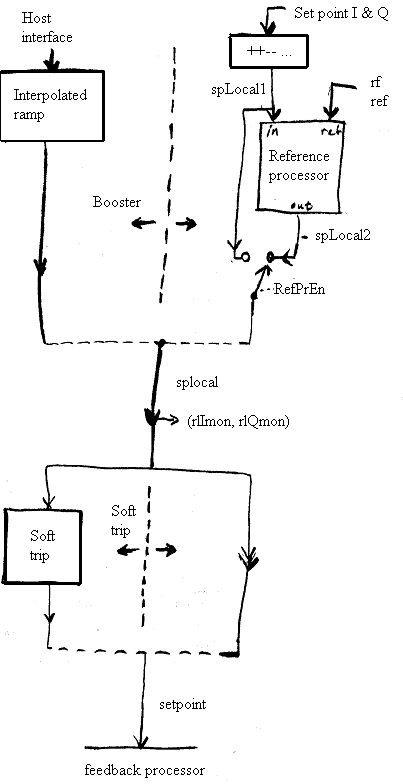

There are a couple of significant differences in the way that feedback set points are handled among the systems. The greatest difference is with the booster rf system where the setpoint is ramped through booster cycles via dedicated logic that interpolates waypoints. The Verilog `define Booster directive instructs the Xilinx logic-development environment to instantiate that module. In builds for all other systems the ramp module is not instantiated and setpoints come from the host as a fixed I/Q pair. The phase of this setpoint is shifted by the phase of the rf reference signal as a means to compensate for drifts of phase shifts of cabling and various signal processing components. Note that in the non-booster systems, when the system requires ramping, it is up to the host to provide it.

Following this first level of setpoint processing, there is the option to insert the soft-trip module, which ramps down the cavity field intensity over an interval that is long compared to the time constant of the cavity. This option is selected by the `define SoftTrip Verilog directive. It is intended for use with the superconducting CESR cavities, but in principle may be used with any cavity equipped with feedback.

This processing scheme and its build options are illustrated in the figure.