Builds for different rf systems

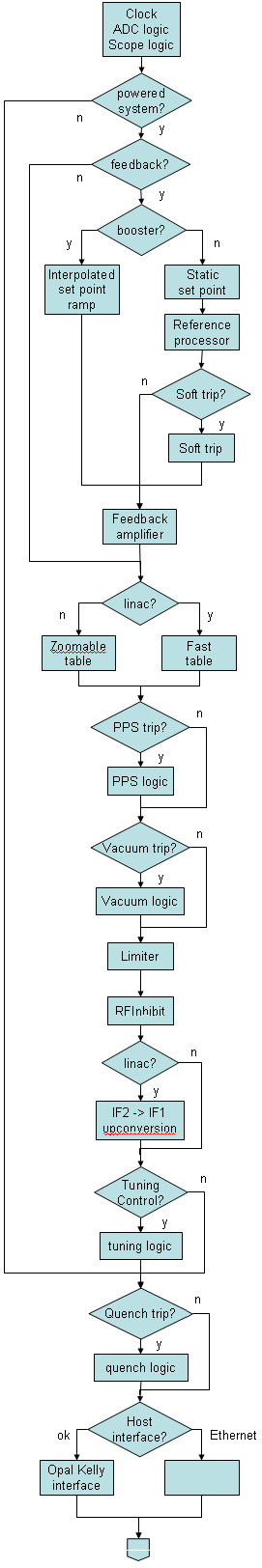

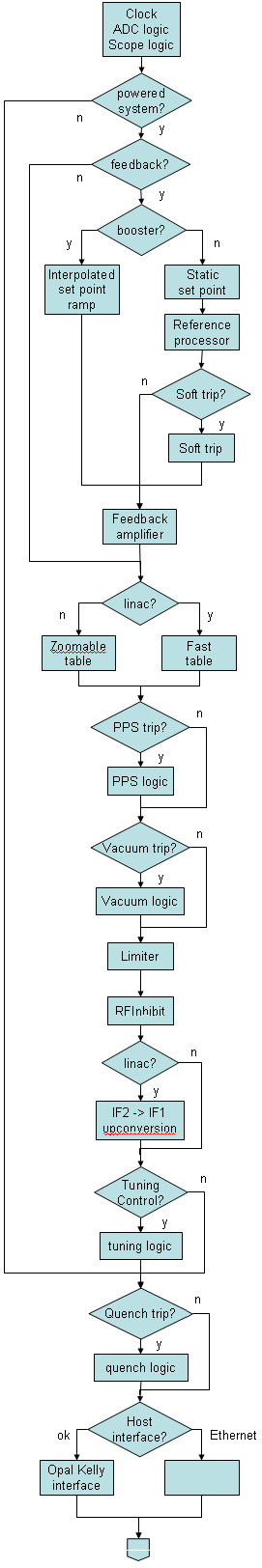

The code for the controller logic has been written so that different rf systems can be flexibly targeted by the compilation of the code. This done through `ifdef .. `else .. `endif and `define compiler directives specifying what options are and are not to be compiled into the build. In code, this level of conditional compilation is reminiscent of block-oriented structured programming of the 1970s, and is amenable to documentation by flow chart. The long figure on the right should be viewed in this context, i.e., as a chart of compiler flow and not of program or signal flow. Thus the source code for the controller logic is by design the same for all the systems, with the exception of the Verilog `defines specifying the target and options. Even board versions with their different external connections are coded, although code for older boards quickly becomes obsolete.

There are several rf systems in NSLS-II targeted by builds of the logic, namely,

- the prebuncher cavities,

- the buncher linac section,

- the main linac section,

- the booster cavity,

- the storage-ring fundamental cavities, and

- the storage-ring harmonic cavities.

They differ substantially in their functions. For example, some of the systems use feedback, while others do not; the storage ring has a soft trip module for controlled ramp downs in response to some trips, while others do not; some systems are even unpowered; and differing interlock needs are accommodated, etc.

When logic is instantiated, it is tied into sources and destinations such as the host interface; when not instantiated, those sources and destinations are available for other uses. These connections are made in the appropriate `if ... `else ... `endif blocks.

Configuration `defines

Below is a list of the symbols that may be defined, and how they affect the build.

- PoweredSystem — When defined, specifies that the rf system is powered, i.e., there is an rf amplifier driving the cavity. As such, logic for the feed-forward setpoint table, upconversion (UpConv.v), interlocks, controls, and readbacks are instantiated.

- Feedback — Specifies that this powered system has feedback. The feedback setpoint table, feedback amplifier (fb_loop.v), and controls and readbacks are intantiated.

- SoftTrip — Specifies that the soft trip module, RampDown.v, is to be intantiated in a powered system with feedback. This module is chained following the feedback setpoint table to, when triggered, ramp the setpoint down to zero prior to a full trip of other components of the rf drive chain to the cavity. Status, host trigger and reset, and status readback of the module are also instantiated. When not specified, the feedback setpoint table output is automatically routed to the feedback amplifier module fb_loop.v.

- ReferenceProcessor — instantiates the reference-processor module in logic.

- Superconducting — signals to the logic that the cavity is superconducting, which makes a difference in fb_loop.v.

- PPS — An interlock block intended to implement PPS interlock, which, like other interlocks, is routed to the RFInhibit block.

- TuningControl — Controls instantiation of cavity tuning controls in logic.

- Vacuum — The on-board serial ADC is to be used to convert an analog signal from a vacuum gauge. That signal is to be used in a feedback loop to control the rf setpoint for vacuum conditioning. This define control whether that logic is instantiated in the build.

- LimitLevel — Sets the level at which the constant-phase limiter limits the rf output.

- QuenchDetection — In a superconducting system, quench detection will probably use the levels and rates of change of forward and reverse power to sense a quench. This function is relevant to both powered and unpowered systems. This `define controls instantiation of that logic.

- InternalFiducial — An external fiducial us used to repeatably align I and Q samples among several rf systems, and specifies when the reference bunch passes. When there is only one rf system, this alignment has no meaning and an external fiducial, even when available, has no function. In such situations there is a need to generate internally a fiducial to which I and Q samples within the logic are aligned. InternalFiducial provides this function.

- The number of clocks per bunch-revolution fiducial is entered in the top-level logic file llrf_xem.v via the Verilog `define BunchRevInterval. If this number is increased to more than 1023, then a counter width must be increased.

- BunchRevInterval – The number of clock cycles between bunch-revolution fiducials.

- TemporaryReference — The rf reference is a signal that undergoes ADC conversion and I/Q detection in parallel with other rf signals, and against which other rf signals within the controller are compared. When a reference is not available a substitute is needed. When TemporaryReference is not defined, the normal signal, perhaps chip 2 port A, is used for the rf-reference role. When TemporaryReference is defined, a fixed signal is generated in logic.

There are defines for different controller-board revisions, although the use of the defines has not be developed.

- BoardRev8 — Controls instantiation of logic specific to board revision 8.

- BoardRev8b — Controls instantiation of logic specific to board revision 8b.

- BoardRev9 — Controls instantiation of logic specific to board revision 9.

Controller board revisions also require revised pin assignments in the llrf_xem.ucf file that is part of the build.

There are also Verilog `defines for specific targets.

- Linac — When the linac is the target, there is no feedback and the feed forward table pulses the drive. This `define controls that the trigger input AVAGO2 is used to trigger the feed forward table.

- Booster — When the booster is the target, there is feedback and the feedback setpoint table ramps the cavity field. This `define controls that the trigger input AVAGO2 is used to trigger the feedback setpoint table to ramp.

- StorageRing — This Verilog `define selects that the trigger input AVAGO2 is used to trigger soft trips.

- HHC — TBD.

- The scope snapshot button displays the scope channels and their Fourier transform in single plots. It also saves the data in the .mat file TestData.mat. When loaded, the variables ScopeCh0, ScopeCh1, ..., ScopeCh7 are in the workspace, each with size 512, 2, consisting of alist of I and Q pairs.

A readback word is allocated to return the states of some of these parameters. See LogicConfiguration.xls for more details. This word is incorporated into the board serial number returned by BoardSerialNumber() implemented in rfboard.m.

The build code

The configuration of the build is available to the host at run time via a 32-bit field of the wire-out readouts. Exact bit assignments are in the configuration spread sheet.

Source code segment configured for the storage ring CESR cavities (1/2012)

/************************** build options ******************************/

// platforms

`define StorageRing

// `define Booster

// `define Linac

// `define HHC

// `define SPB

// `define PBU

// `define MO

`ifdef MO // for Master Oscillator version

`define Linac

`define ofl_value 20

`else

`define ofl_value 0

`endif

`ifdef HHC

`define Superconducting // for superconducting cavity

`else

`define PoweredSystem // powered systems

`ifndef Linac

`define Feedback // systems with feedback

`ifdef StorageRing

`define SoftTrip // soft-trip logic (RampDown.v)

`define ReferenceProcessor // reference processor

`define Superconducting // for superconducting cavity

// `define ffRampInterval // diagnostic mode; comment for ff zoom control

`endif

`ifdef Superconducting

`define sibits 5 // fb_loop bit parameter: SC

`else

`define sibits 7 // fb_loop bit parameter: NC

`endif

`endif

`endif

`define InternalFiducial // bunch fiducial, from AVAGO1 or synthetic

// `define TemporaryReference // temporary internal reference

`define Quench // SC quench detection

// `define Vacuum // vacuum interlock and/or conditioning

`define TuningControl // tuning phase error and control

`define PPS // another interlock module

`define LOAboveRF // LO frequency is greater than RF frequency

`define LimitLevel 5276 // limiter level

`define BunchRevInterval 528 // clocks between bunch revolution fiducial

// `define ChannelTest // for testing of the ADC channels

`define OpalKelly // Opal Kelly vs ethernet

/***********************************************************************/