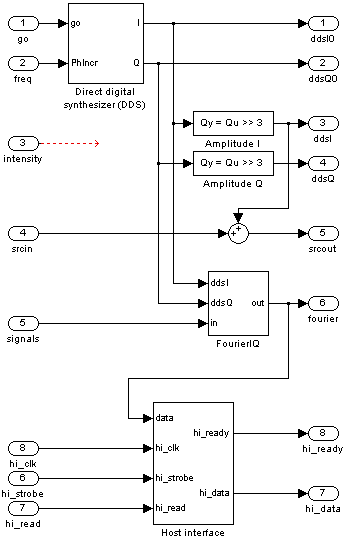

This module acts as a network analyzer: it generates a synthesized (DDS) sine wave for excitation of a system being measured, and Fourier analyzes one or more signals from the system for their response functions from the point of excitation. The Fourier analysis consists of computation of sine and cosine integrals over a specified integral number of cycles of the sine wave, after a specified dead time allowing transients to die away. To excite a system, the sine wave generated by the DDS is added to a signal passing in and out through a pair of ports. The intensity of the excitation may be selected as a power of two. The DDS is useful for excitation frequencies within about ±fs/200 of the I/Q IF frequency (IF2). Up to 15 signal channels may be intantiated, the number determined by a parameter specified at build time.

The DDS frequency is selected via numerical logic input vectors, as are the duration of integration and damping time. The sine and cosine integrals are accessible by the host through a throttled pipe. The up to 30 integrals are transferred as a block (illustrated below), each integral as a double word, along with a double word containing the integration time as a clock count, and a filler double word. The block size transferred is 32 double words (128 bytes) regardless of the number of channels instantiated.

I1, Q1 I2, Q2 ... Inchans, Qnchans 0, 0 ... 0, integration time

| clk | input | The clock input. |

| reset | input | The reset input, used return the network analyzer to the idle state, including stopping DDS output. |

| go | input | Arm/trigger vector that initiates an analysis sequence. A single bit simply triggers the start. |

| gonow | output | Is asserted for a clock when the final trigger condition is met. This is the pulse that finally initiates an analysis sequence. |

| quad | input | The I/Q quadrant fiducial. |

| freq | input | The frequency in terms of the phase increment on the 2wpi scale of the DDS phase accumulator, which is incremented every clockinterval clocks. |

| acquirecount | input | Integration time as a count of DDS modulation cycles (DDS turns). |

| dampcount | input | Delay time between the time the DDS starts at the current frequency, and the start of integration. It is an integer count of DDS modulation cycles (turns). |

| ddsI0, ddsQ0 | output | The I and Q outputs of the DDS. These signals are the provided to the fourier analyzers. |

| ddsI, ddsQ | output | The two DDS outputs upconverted to fs/4. |

| signals | input | The signals in I/Q data streams to be analyzed. There are nchans of them concatenated into a single vector. |

| fourier | output | The output Fourier cosine and sine integrals. There are 2*nchan of them concatenated into a single vector. |

| busy | output | Indicates that a measurement sequence is in progress, including the leading dead time. |

| ddstick | output | Asserted for one clock cycle to indicate that the DDS has generated a fresh I/Q vector. |

| turntick | output | Asserted for one clock cycle to indicate that the baseband DDS has completed a turn. |

| valid | output | Asserted for one clock cycle to indicate that an analysis sequence has completed and the fourier data are available for readout. |

| intensity | output | The intensity of the DDS output. The DDS output is scaled downward by powers of two selected by intensity: dds = 215-intensity × full scale. |

| srcin | input | A system I/Q data stream to which is added the dds excitation. |

| srcout | output | The srcin port with the scaled dds excitation added. |

| hi_clk | input | Host clock of the host interface. |

| hi_strobe | input | Indicates that the host is initating a read sequence. |

| hi_ready | output | Indicates that the logic is ready to provide data to the host. |

| hi_read | input | Asserted by the host when reading data from the data port. |

| hi_data | output | Provides data to the host. |

Parameters, their defaults, and descriptions:

| nchans | 1 | The number of signals concatenated in the signals vector to be analyzed. |

| wd | 15 | The bit width of the signals to be analyzed. |

| wdds | 15 | The bit width of the dds ports ddsI,Q and ddsI0,Q0. |

| wo | 24 | The bit widths of the Fourier integrals in ports fourier and meas. |

| wl | 11 | The bit width of the clockinterval port representing clocks between dds phase increments. |

| wpi | 13 | The bit width of the phase-increment port PhIncr. |

| wpa | 20 | The bit width of the phase accumulator internal to the dds. The port PhIncr is added to this accumulator every clockinterval clock cycles. |

| wtc | 10 | The bit width of the turn counter. |

| ofl | wtc | The number of integrator overflow bits. It should be large enough that the accumulator will not overflow during the analysis cycle. The value wpc may be a good choice. |

| apb | 12 | The number of accumulator precision bits. These least-significant bits are used during accumulation but discarded from the output as a means to control accumulated quantization error. The value ofl/2 is often a good choice. |

| wi | 4 | The intensity-port bit width. It need not be greater than ceiling(log2(wdds)). |

| ws | 15 | The bit widths of the ports srcin and srcout. |

| whi | 16 | The host-interface bus width. |

| ws | 15 | The source input and output bit width. |

| si | wdds+1 | The interval between DDS output updates. |

freq = f × si × 2wpa/ fswhere fs is the sample rate. The frequency is limited by the largest value freq can hold, roughly ±2wip-1.

fmax = fs/(si 2wpa-wpi+1)

localparam chans = 3, // number of channels

wd = 15, // signals to be analyzed

ws = 14, // through ports

wdds = 12, // dds width

wo = 24, // fourier output

wpa = 19, // phase accumulator

wpi = wd, // phase increment (frequency)

wtc = 11, // turn counter

ofl = 20, // overflow

whi = 16; // host interface

// network analyzer setup parameters

wire [wtc-1:0] dampingtime, integrationtime;

wire signed [wpi-1:0] frequency;

wire [wi-1:0] intensity;

// DDS outputs

wire signed [wdds-1:0] I0, Q0; // unscaled

wire signed [wdds-1:0] I, Q; // scaled

// input signals to be analyzed

wire [wd-1:0] sig1, sig2, sig3;

// through ports into which dds is injected

wire signed [ws-1:0] din, dout;

// host interface ports

wire hi_clk, hi_strobe, hi_ready, hi_read;

wire [whi-1:0] hi_data;

NetworkAnalyzer

#(.nchans(chans), .wd(wd), .ws(ws), .whi(whi), .wdds(wdds),

.wo(wo), .wpa(wpa), .wpi(wpi), .wtc(wtc), .ofl(ofl))

na (

.clk(clk), .reset(stoppulse),

.go(startpulse), .gonow(nagonow),

.quad(quadrantfiducial),

.freq(frequency), .dampcount(dampingtime),

.intensity(intensity), .acquirecount(integrationtime),

.ddsI0(I0), .ddsQ0(Q0), // unscaled

.ddsI(I), .ddsQ(Q), // scaled

.signals({sig3, sig2, sig1}),

.busy(naBusy), .ddstick(ddst),

.turntick(nact), .valid(naValid),

// ff data stream

.srcin(din), .srcout(dout),

// host interface

.hi_clk(hi_clk), .hi_strobe(hi_strobe),

.hi_ready(hi_ready), .hi_read(hi_read),

.hi_data(hi_data)

);