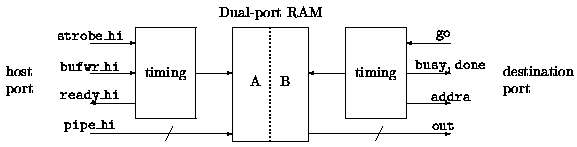

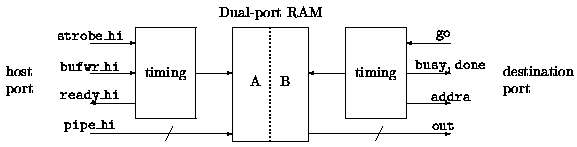

This module provides a table that is output without interpretation for use as a feed-forward table in linac or other builds where a higher data rate is required. The idea is that, unlike the module Table, the table is clocked at the full DAC rate, outputting data at the first IF frequency (IF1) and obviating the need for separate upconversion to that IF frequency. To do this, pre-upconverted samples are provided to the table via the host port of the two-port buffer. The module Table.v used in other builds accepts baseband I/Q pairs and upconverts to the IF2 frequency, which is later upconverted to IF1 using Doolittle's method. The buffer has 1024 sixteen-bit word capacity, and the second (host-interface) port implements the Opal Kelly block-throttled pipe having handshaking for controlling data flow. When triggered, the contents of the buffer is output. When finished, the last 2w2 words are repetitively output.

Ports | Parameters | Notes | Example | Diagram

| clk | input | The data clock input. |

| reset | input | The reset input. |

| go | input | A gb-bit trigger vector (defaults to one bit). The bits successively arm the module, the last bit actually triggering it. |

| gn | output | The final trigger pulse initiating table output. |

| trigstate | output | Vector of bits indicating the current state of the trigger logic. The first (most-significant) bit is the idle state, while the last (least-significant) bit is the final arm state. |

| addra | output | An address counter indicating which sample of the table is being output (0 to 2w1-1). |

| out | output | Table output (wd bits). |

| busy | output | When asserted, indicates the table is currently outputing its data. It goes high with gn, not go. |

| done | output | Is asserted for one clock indicating that the table has been output and the sequence is ended. |

| clk_hi | input | Host-interface clock. |

| ready_hi | output | A handshaking signal asserted by TableFast indicating that it is ready to receive data. When asserted, the host is free to apply data to pipe_hi and assert bufwr_hi. When this signal is deasserted, the host must deassert bufwr_hi and cease the transfer. |

| strobe_hi | input | Asserted briefly by the host indicating that it is initiating a transfer sequence. It does not indicate data are valid on pipe_hi, which must only occur when ready_hi is asserted by TableFast. |

| bufwr_hi | input | Asserted by the host interface indicating that data are currently valid on pipe_hi. |

| pipe_hi | input | The data from the host. |

| w1 | 10 | Width of the address counter. The number of words in the table is 2w1, which must not exceed 210. |

| w2 | 2 | Width of the waypoint address counter. |

| wd | 16 | Width of the data input and output by this module. It can be at most 18, a limit set by the dual-port memory primitive. |

| gb | 1 | Width of the trigger-logic go and trigstate ports for multi-bit triggers (see the trigger module). |

localparam wd = 15;

wire clk, reset, go, gn, busy, done;

wire [wd-1:0] data;

wire clk_hi, ready_hi, busy_hi, done_hi;

wire strobe_hi, wr_hi;

wire [wd-1:0] data_hi;

TableFast #(.wd(wd))

ffTable (

.clk(clk), .reset(reset),

.go(go), .gn(ffgn),

.busy(busy), .done(done),

.out(data),

// host interface

.clk_hi(clk_hi), .ready_hi(reeady_hi),

.strobe_hi(strobe_hi), .bufwr_hi(wr_hi),

.busy_hi(busy_hi), .done_hi(done_hi),

.pipe_hi(data_hi)

);