This module implements 1-wire bus-master reset/presence cycles, cycles that resets a 1-wire device, and allows the device to signal its presence. In this cycle, the bus master pulls the 1-wire bus low for a long period (~0.5 ms) and a listens for a response (bus pulled low) from the device during the following 0.5 ms. The module implements this cycle and flags the completion of the cycle and the device's presence via two output ports. Parameters control intervals in the cycle in terms of the clock frequency. The defaults apply to a 1-MHz clock.

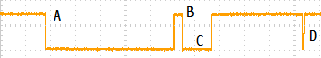

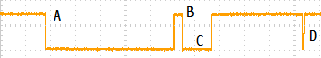

The figure illustrates the cycle. Timebase divisions are at 100-μs intervals. The module pulls the bus low (A) for about 0.5 ms and releases. The device senses the release and pulls the bus low (B) for a time indicating it is present. The module then senses presence by sampling the bus at C. The point D indicates the start of another bus cycle, a short time after the end of the reset/presence cycle. The duration of the entire cycle is about 1 ms.

Ports | Parameters | Notes | Example | Timing diagram

| clk | input | The clock input. |

| reset | input | The reset input. |

| go | input | Command to initiate a cycle. |

| dq | in/out | The 1-wire bus. It is configured to go high when undriven. |

| present | output | Indicates that a device responded to the cycle. |

| busy | output | Indicates that the cycle is in progress. |

| done | output | Asserted for a clock when the cycle is completed. |

| w1 | Bit width of the timer for the low-pulse duration (default 9). |

| t1 | Low-pulse duration in clocks (default 512). It must not be greater than 2w1. |

| w2 | Bit width of the timer for the presence-sampling time C (default 7). |

| t2 | Interval in clocks between the end of the low pulse and presence sampling at C of the figure (default 70). It must not be greater than 2w2. |

| w3 | Bit width of the timer for the duration of the remainder of the cycle following the low pulse (default w1). |

| t3 | Duration of the remainder of the cycle following the low pulse (default t1). Must be at most 2w3. |

// test for device presence

tri onewire;

wire present, busy, done;

owResetPresence hello (

.clk(clk), .reset(reset),

.go(go), .dq(onewire),

.present(present),

.busy(busy), .done(done)

);